이번에는 정보처리기사 필기 과목인 전자계산기 구조의 플리플롭을 알아보아요.

플리플롭

입력과 클럭(Clock)에 따라 상태가 변하는 순서 논리회로

클럭(Clock) 펄스가 발생하지 않으면 상태가 변하지 않습니다.

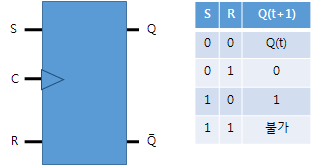

RS 플리플롭

이전 클락의 값을 유지하거나 0 혹은 1로 설정하는 플립플롭

S은 설정 입력 값이며 R은 리셋 입력 값입니다.

S와 R이 0이면 이전 상태를 유지합니다.

S와 R을 1로 입력할 수 없습니다.

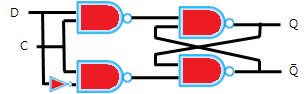

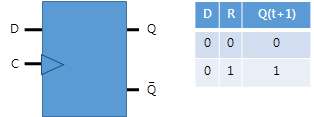

D 플리플롭

Delay 플리플롭입니다.

입력한 값을 다음 클락의 출력으로 지연하는 플립플롭입니다.

RS 플리플롭의 R값을 S의 NOT(인버터)으로 사용하는 플리플롭입니다.

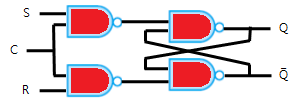

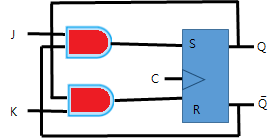

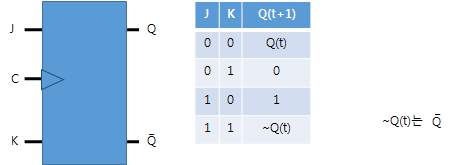

JK 플리플롭

RS 플리플롭에서 R과 S를 동시에 1을 입력하지 못하는 것을 보완한 플리플롭입니다.

RS 플리플롭에서 R과 S가 동시에 1일 때 Q(t)의 부정(Inverter)를 출력하게 보완한 플리플롭입니다.

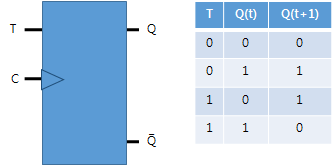

T 플리플롭

토클(Toggle) 플리플롭입니다.

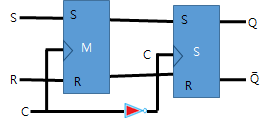

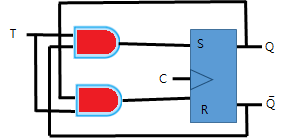

주종 플리플롭

마스터 RS 플리플롭과 슬레이브 RS 플리플롭으로 구성한 플리플롭입니다.

마스터 – 슬레이브 플리플롭이라고 부릅니다.

플리플롭에서 발생하는 경쟁(Race) 현상을 없애기 위한 플리플롭입니다.

경쟁(Race) 현상은 출력값을 입력값으로 사용하는 피드백 과정에서의 불안정한 상태를 말합니다.