이번에는 정보처리기사 필기 과목인 전자계산기 구조의 마이크로 연산을 알아보아요.

마이크로 명령 형식

수평 마이크로 명령: 마이크로 명령의 한 비트가 한 개의 마이크로 동작에 관한 명령

수직 마이크로 명령: 마이크로 명령어의 코드화된 비트를 해독하는 디코딩 회로를 이용하여 제어 신호를 사용

한 개의 마이크로 명령으로 한 개의 마이크로 동작만 제어할 수 있음

제어 기억장치의 용량을 줄일 수 있습니다.

나노 명령: 낮은 레벨의 나노 메모리에 저장한 마이크로 명령을 말합니다.

마이크로 Cycle Time

마이크로 연산을 수행하는데 걸리는 시간

CPU Clock Time 또는 CPU Cycle Time으로 부르기도 합니다.

CPU Clock

CPU의 순서 동작을 동기화하기 위한 Clock 펄스

마이크로 Cycle Time은 CPU Clock의 발생 주기와 동기화를 해 주어야 합니다.

마이크로 연산(Micro Operation)

명령을 수행하기 위해 CPU내의 레지스터와 플래그의 상태 변환이 발생하는 동작

기억장치로부터 명령어를 인출하여 해독하고 해독한 명령어를 수행하기 위해 제어 신호를 발생하는 각 단계의 세부 동작

하나의 명령어는 여러 개의 마이크로 연산으로 수행합니다.

레제스터에 있는 데이터를 사용하여 동작합니다.

CPU내에서 순서적으로 수행하게 하는 것은 제어 신호입니다.

*동기 디지털 시스템의 모든 내장 레지스터의 타이밍은 마스터 클락 발생기에 의해 제어합니다.

동기 고정식(Synchronous Fixed) 사이클 시간

CPU Clock 주기를 Micro Cycle Time과 같게 정의하는 방식

모든 마이크로 연산을 수행하는 시간이 같다고 가정합니다.

따라서 가장 긴 마이크로 연산 시간을 Micro Cycle Time으로 정합니다.

동기 가변식(Synchronous Variable) 사이클 시간

비슷한 수행 속도를 갖는 마이크로 연산을 클래스화 하여 Micro Cycle Time을 정합니다.

같은 클래스에 있는 마이크로 연산의 Micro Cycle Time은 같습니다.

비동기식(Asynchronous) 사이클 시간

마이크로 연산에 따라 서로 다른 Micro Cycle Time을 정의합니다.

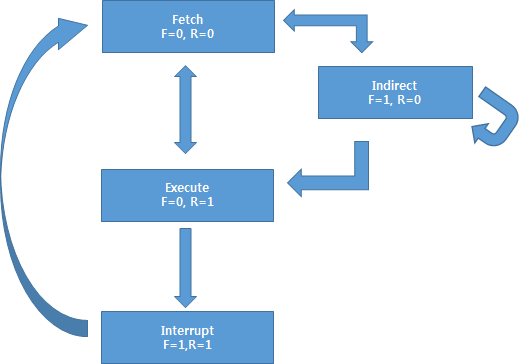

CPU 메이저 상태(Major State)

Fetch, Excute, Indirect, Interrupt 상태가 있습니다.

메이저 스테이트 레지스터를 통해 알 수 있습니다.

Major 상태 사이클(Major State Cycle)

CPU의 상태 변화 사이클을 말합니다.

기계 사이클(Machine Cycle)이라고도 부릅니다.

Fetch Cycle

명령어를 주기억장치에서 CPU의 IR(Instruction Register)로 가져와 해석하는 단계로 제일 먼저 진행합니다.

MAR ← PC 프로그램 카운터(PC)에 있는 명령어를 메모리 주소 레지스터(MAR)에 전송

MBR ← M[MAR], PC ← PC+1메모리의 MAR 위치의 값을 MBR(Memory Buffer Register)로 전송하고 PC 1 증가

IR ← MBR[OP], I ← MBR[I] 명령어의 OP 코드를 IR(Instruction Register)에 전송, 명령어의 모든 비트를 I 플립플럽에 전송

다음은 I값에 따라 수행이 달라집니다.

F ← 1 I 값이 0(직접주소)이면 Excute Cycle로 상태 전이(F ← 1, R ← 0)

R ← 1 I 값이 1(간접주소)이면 Indirect Cycle로 상태 전이(F ← 0, R ← 1)

Indirect Cycle

주소필드(Operand 부)의 주소를 읽는 단계

MAR ← MBR[AD] MBR에 있는 명령어의 주소를 MAR에 전송

MBR ← M[MAR] 메모리의 MAR 위치의 값을 MBR에 전송

1Cycle 명령이면 Fetch Cycle로 상태 전이합니다.(F ← 0, R ← 0)

실행 명령이면 Excute Cycle로 상태 전이합니다. (F ← 1, R ← 0)

Excute Cycle

Fetch에서 해석한 명령을 실행하는 단계

플레그 레지스터의 상태 변화에 따라 Interrupt 단계로 상태 전이합니다.(F ← 1, R ← 1)

플레그 레지스터의 상태 변화가 없으면 Fetch Cycle로 상태 전이합니다.(F ← 0, R ← 0)

Interrupt Cycle

인터럽트 발생 단계

MBR[AD] ← PC, PC ← 0 MBR 주소 부분에 PC값을 전송, PC를 0으로 설정

MAR ← PC, PC ← PC+1 PC값을 MAR에 전송, PC를 1 증가

M[MAR] ← MBR, IEN ← 0 MBR을 메모리 MAR 위치에 저장, IEN(Interrupt Enable 플리플롭)에 0을 전송

Fetch Cycle로 상태 전이(F ← 0, R ← 0)